# Nonlinear III-V HBT Compact Models: Do We Have What We Need?

Jonathan Scott, Microwave Technology Center, Agilent Technologies, 1400 Fontaingrove Parkway, Santa Rosa, CA, 95404, USA. [jonathan\\_scott@agilent.com](mailto:jonathan_scott@agilent.com)

**Abstract**— Within the large body of literature on models for III-V HBTs it now seems possible to find compact formulations with extractable parameters that model all important device characteristics. Predictions are as accurate as possible given the limitation of quasi-static host simulators. Some recommended strategies for extraction of parameters for certain formulations are given. Despite accurate formulation, some aspects may be better left out of models in the interest of expediency, with no significant reduction of final performance. Transit time remains difficult, and limitations of simulators swamp discrepancies between measurement and predictions of even apparently-precise models. It is concluded that compact models, if not simulators, are as physically precise as we should bother to make them.

## I. INTRODUCTION

MODELING Heterojunction Bipolar Transistors, particularly in the III-V family, is a challenge that has spawned over 100 publications in well-respected journals over the last 10–15 years. The majority address the design of a compact model, typically physically-based, for use in contemporary simulators such as SPICE or ADS, and the extraction of parameters for such models. One might expect that by now the literature would contain enough wisdom for a satisfactory model to have become clear, even if all facets of this Gestalt-model were not to have been collected in one citation. This proposition is examined here.

## II. DC MODEL

Most complete, large-signal, compact, III-V HBT models in the literature (for example see [1]–[7]) employ a small, separate subcircuit to model self-heating (at least in the case of a single device in thermal isolation from other dissipators), after the fashion of the VBIC model[8]. The dc collector current in forward-active operation is computed from three voltages, the (intrinsic) base-emitter voltage  $v_{be_i}$ , the (intrinsic) base-collector voltage  $v_{bc_i}$ , and the voltage found from the thermal subcircuit and which represents instantaneous device temperature,  $v_{Tj}$ .

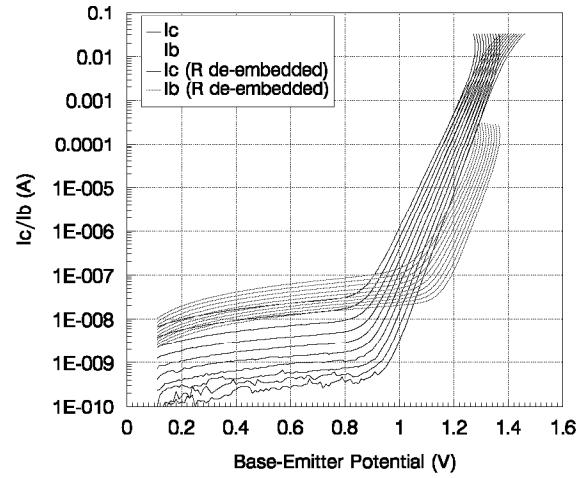

Figure 1 is a Gummel plot for an HBT with an emitter area of  $16\mu\text{m}^2$  for substrate temperatures of 15–105C. Note that both the “extrinsic” and “intrinsic” data are plotted. It is immediately obvious that the curvature of the extrinsic data must be signifi-

Fig. 1. Gummel plot for an InGaP/GaAs HBT with an emitter area of  $16\mu\text{m}^2$  for substrate temperatures of 15–105C.

cantly altered by the parasitic resistances and device self-heating. These go in opposite direction, and the curvature of the measured result is deceptively mild.

The UCSD model[5] has the transfer-current form

$$I_{cc} = \frac{I_{sf}(T_j) e^{\frac{v_{be_i}}{N_f V_T}} - I_{sr}(T_j) e^{\frac{v_{be_i}}{N_r V_T}}}{q_1 \frac{(1+\sqrt{4q_2+1})}{2} + I_{sa}(T_j) e^{\frac{v_{be_i}}{N_a V_T}} + I_{sb}(T_j) e^{\frac{v_{be_i}}{N_b V_T}}} \quad (1)$$

where base-width modulation or Early effect and high-level injection/knee-current or Webster effect are modeled as in the case of silicon, should they be significant, through the action of  $q_1$  and  $\frac{1}{2}(1 + \sqrt{4q_2 + 1})$  respectively; the saturation currents may be adjusted dynamically for junction temperature  $T_j$  according to [2]:

$$I_s(T_j) = e^{[\ln(I_s) + (1 - \frac{T_{ref}}{T_j}) \frac{T_s}{T_{ref}}]} \quad (2)$$

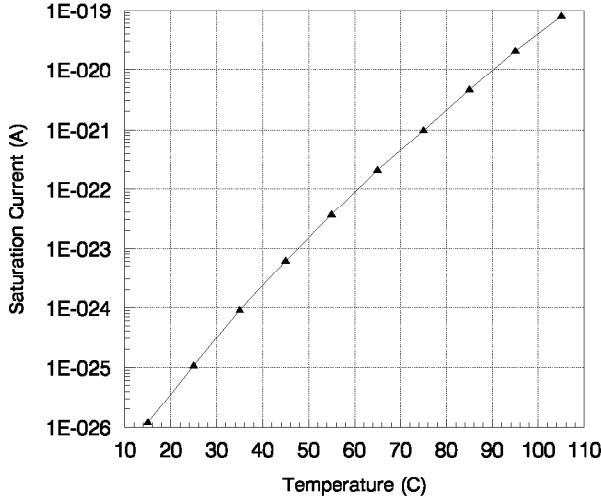

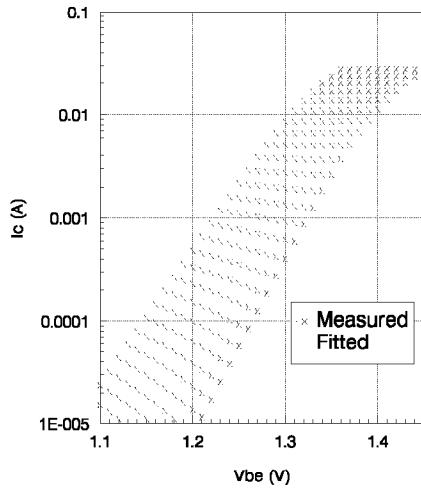

Numerical fitting applied initially to data at each temperature, and subsequently to all the Gummel plots simultaneously, yields saturation current variation as shown in figure 2, and finally the agreement shown in figure 3. In this fit, the Webster term is switched off ( $q_2 = 0$ ) and the reverse terms negligible, but the forward “heterojunction” term in the denominator is required for the equation to fit for

Fig. 2. Plot of saturation current  $I_{sf}$  against temperature, resulting from numerical fitting of equations 1 and 2 to the measured data in figure 1.

Fig. 3. Plot of measured data and model prediction of collector current from equations 1 and 2.

higher current densities. Almost as good a fit can be obtained, for practical current densities, without the forward “heterojunction” term but with the Webster term pressed into service in its place.<sup>1</sup> In summary, dc, collector-current models are excellent, but absolutely demand precise allowance for temperature and terminal resistances. For the above fit,  $R_{th}$  and  $R_{ee}$  are required and must be accurate to a few percent;  $R_{bb}$  is less critical as its effect is smaller, and  $R_{cc}$  becomes significant only in saturation characteristics.

The extraction of thermal resistance,  $R_{th}$ , has been recently addressed elsewhere.[9] Experience

<sup>1</sup>This is physically “incorrect”, as the Webster term effectively forces the current in the absence of resistive and thermal effects towards an asymptote with slope corresponding to an ideality factor of 2, but the UCSD-model “heterojunction” term does not constrain the asymptote slope.

suggests that the extraction of  $R_{ee}$  is most effective using a technique based on [10] but additionally taking care to repeat extrapolation in the reciprocal-current domain for separate frequency-temperature pairs and *with allowance for device self-heating*. The reader must take the author’s word for this in the interest of respecting the page limit.

The modeling of base current is less prominent in the literature, and even multi-diode models such as that in [1] achieve slightly less exact a fit than in the case of collector current. This may stem from the fact that many HBT processes suffer relatively large shifts in base-current characteristics with time. The reader must also take the author’s word for this in the interest of respecting the page limit.

A recent discussion of breakdown appears elsewhere,[14] and so is omitted here.

### III. CHARGE-STORAGE MODEL

Suitable calculations made on measured S-parameter data readily distinguish device capacitance and transit time.[11], [12] With less reliability, base and collector transit times may be distinguished.[13] Simulators running compact models ultimately need to know node currents (and conductance and transconductances), as well as node stored charge (and capacitance and transcapacitances) as a function of node voltages. It is critical to note here that once equations are selected to model the stored charge arising from capacitive and transit effects, their return values must be assigned to nodes (branches) and all the charges on any given node (branch) summed and treated identically. Thus *it will never be possible to distinguish the provenance of a charge from S-parameter data derived from the model* as was the case with measured data. E.g., figure 6 can never be reproduced faithfully using data from simulation.

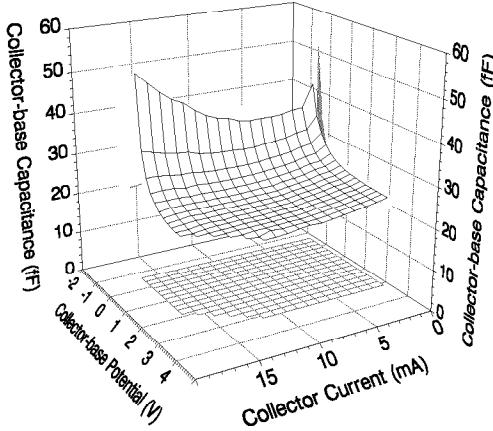

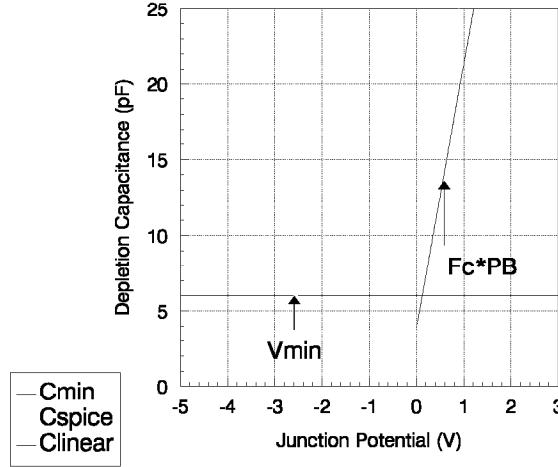

In selecting equations to model charge stored in capacitance and transit, approaches in the literature are less unified. The UCSD model, whose charge storage part is largely attributed to Camnitz[4], uses a reasonably well-accepted model for capacitance but with the addition of the possibility that  $C_{bc}$  will be modulated by collector current. Figure 4 shows the variation of  $C_{bc}$  with both voltage and current. The latter effect is perceptible, but barely so. The variation with voltage is well modeled by the usual SPICE equation with linear extension for voltages approaching the built-in potential, and with a minimum value reached at punch-through. Various publications implement this differently (for example [1] uses a root-of-sum-of-powers smooth maximum function, [5] a continuous but not differentiable piecewise function) but the effect is equivalent. Figure 5 illustrates the UCSD-style piecewise model.

Fig. 4. Plot of  $C_{bc}$  as a function of voltage and current. Note the projections on the axis planes that assist visualization of the surface.

Fig. 5. Plot of depletion capacitance against junction voltage, showing the “discrete regions” (minimum or punched-through, SPICE-like, and linearly extrapolated) involved. The final capacitance follows the SPICE formulation in the middle region.

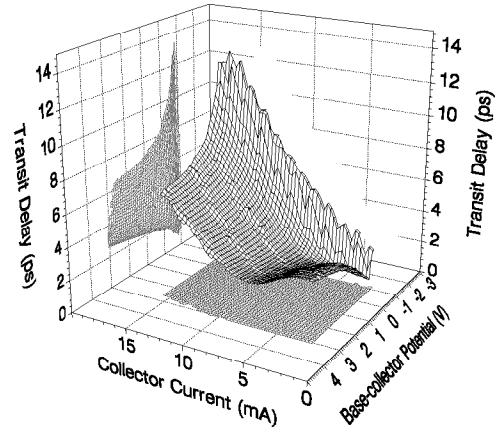

Figure 6 is a surface plot of transit time extracted in the usual way[15] from an HBT similar to that used previously. No completely suitable modeling formulation seems to be available in the literature. The best formulation is perhaps the strongly physical one in [16], but being chiefly aimed at silicon devices, it does not incorporate “ $f_T$  peaking”, which accounts for the dip visible in figure 6 for mid-currents and higher voltage. The UCSD model in [5] does potentially incorporate  $f_T$  peaking but otherwise relies on equations that have no strong physical basis, and whose parameters are difficult to extract. Apart from the peaking phenomenon, however, equations culled from [16] are effective at reproducing the data and

Fig. 6. Plot of measured transit time ( $\tau_B + \tau_C$ ) as a function of voltage and current, again on a  $16\mu\text{m}^2$  HBT. Note the projections on the axis planes that assist visualization. Values have been computed from S-parameter data measured under short pulsed-I/V conditions.

have extractable parameters.

Difficulties can arise because transit charge storage is a function of temperature. Realize that the small-signal data from which points on the surface in figure 6 are computed has been measured across a range of bias values. If carried out with steady-state rather than pulsed bias, the device temperature would vary significantly across the same surface. Thus pulsed-S-parameters should be used to obtain isothermal data.

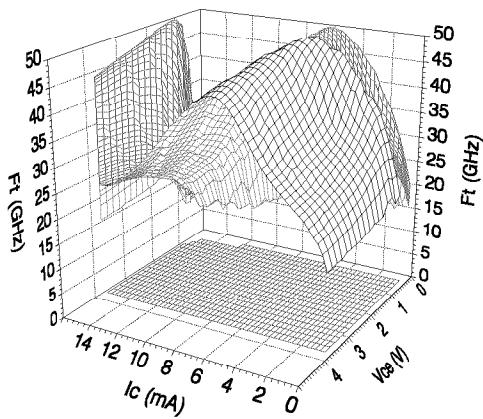

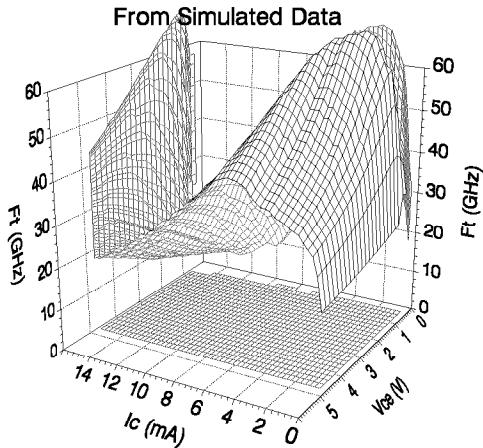

A new transit-charge formulation<sup>2</sup> that very faithfully reproduces the data in figure 6 yields only a fair model. Because charges are superimposed, the model can never act as did the device even if it “knows” both capacitive and transit charges exactly. As example we might compare transit frequency (refer to figures 7 and 8): The agreement is fair to poor, not excellent like the values that went into the model. A more rigorous comparison involves looking at devices of different structure, parameters other than transit frequency<sup>3</sup>, and circuits as well as discrete transistors, and cannot appear here.

#### IV. CONCLUSIONS

HBT models can be “excessively” accurate, including effects that may not be perceptible in devices. Model simplification in the interest of computational efficiency is appropriate in this case.

There is published evidence of phenomena operating in III-V HBTs that have not been addressed in the modeling literature, and so models do not prop-

<sup>2</sup>The new formulation is not yet in the public domain.

<sup>3</sup>The use of transit frequency represents the selection of a weighting scheme for scalar comparison of the 4 complex numbers that comprise 2-port S-parameters at each bias.

Fig. 7. Surface plot of transit frequency extracted from the same data used for figure 6.

Fig. 8. Surface plot of transit frequency extracted from S-parameters obtained from a compact model fitted to the data used for figure 6, in which both capacitances and transit times are accurately modeled.

erly embody device response in such areas as base current for higher junction current density, or fine structure of collector current as a function of base-collector voltage. It could be argued that these effects barely impact many designs, or that designers do not expect such precision from simulations.

It has been shown that simulator inability to properly model transit charge can dominate prediction error. *This can negate any benefits expected from a superior model formulation.*

It is suggested that a good, if not perfectly satisfactory, model can be composed from what is available today in the literature. This conclusion might not hold true for a model that is not constrained to be quasi-static.

## REFERENCES

- [1] Christopher M. Snowden, "Large-Signal Microwave Characterization of AlGaAs/GaAs HBT's Based on a Physics-Based Electrothermal Model", *IEEE Transactions on Microwave Theory and Techniques*, vol. 45, no. 1, January 1997, pp58–71.

- [2] P Chris Grossman and John Choma, Jr., "Large-Signal Modelling of HBTs Including Self-Heating and Transit Time Effects", *IEEE Transactions on Microwave Theory and Techniques*, vol. 40, no. 3, March 1992, pp449–464.

- [3] Ke Lu, Philip A. Perry and Thomas J. Brazil, "A New Large-Signal AlGaAs/GaAs HBT Model Including Self-Heating Effects, With Corresponding Parameter-Extraction Procedure", *IEEE Transactions on Microwave Theory and Techniques*, vol. 43, no. 7, July 1995, pp1433–1445.

- [4] Lovell H. Camnitz, Steve Kofol, Ton Low, and Sandeep R. Bahl, "An Accurate, Large Signal, High Frequency Model for GaAs HBTs", *GaAs IC Symposium Proceedings*, 1996, pp303–306.

- [5] UCSD Model, UCSD Electrical and Computer Engineering Department, "<http://hbt.ucsd.edu/>", revision 9, 10/95.

- [6] Ce-Jun Wei, James C. M. Hwang, Wu-Jing Ho, and J. Aiden Higgins, "Large-Signal Modeling of Self-Heating, Collector Transit-Time, and RF-Breakdown Effects in Power HBT's", *IEEE Transactions on Microwave Theory and Techniques*, vol. 44, no. 12, December 1996, pp2641–2647.

- [7] M. Rudolph, R. Doerner and P. Heymann, "New GaInP/GaAs-HBT Large-Signal Model for Power Applications", *European Microwave Conference Digest*, 1998, pp231–235.

- [8] Colin C. McAndrew, Jerold A. Seitchik, Derek F. Bowers, Mark Dunn, Mark Foisy, Ian Getreu, Marc McSwain, Shahriar Moinian, James Parker, David J. Roulston, Michael Schröter, Paul van Wijnen, and Lawrence F. Wagner, "VBIC95, The Vertical Bipolar Inter-Company Model", *IEEE Journal of Solid-State Circuits*, vol. 31, no. 10, October 1996, pp1475–1483.

- [9] Jonathan Scott, "Reconciliation of Methods for Bipolar Transistor Thermal Resistance Extraction" To be presented at *ISCAS 2001* Sydney, May 2001.

- [10] S. A. Maas and D. Tait, "Parameter-Extraction Method for Heterojunction Bipolar Transistors", *IEEE Microwave and Guided Wave Letters*, vol. 2, no. 12, December 1992, pp502–504.

- [11] D. R. Pehlke and D. Pavlidis, "Evaluation of the Factors Determining HBT High-Frequency Performance by Direct Analysis of S-Parameter Data", *IEEE Transactions on Microwave Theory and Techniques*, vol. 40, no. 12, December 1992, pp2367–2373.

- [12] Allan P. Laser and David L. Pulfrey, "Reconciliation of Methods for Estimating  $f_{max}$  for Microwave Heterojunction Transistors", *IEEE Transaction on Electron Devices*, vol. 38, no. 8, August 1991, pp1685–1692.

- [13] Mohammad Sotoodeh, A. H. Khalid, Hong Sheng, Farid A. Amin, Takar Gokdemir, Ali A. Rezaad, Andy P. Knights and Christopher C. Button, "Direct Extraction and Numerical Simulation of the Base and Collector Delay Times in Double Heterojunction Bipolar Transistors", *IEEE Transactions on Electron Devices*, vol. 46, no. 6, June 1999, pp1081–1086.

- [14] Jonathan Scott and Tom Low, "Avalanche Breakdown in HBTs: Variation with Collector Current and Effect on Linearity" *IEEE GaAs IC Symposium Digest*, November 2000.

- [15] H.-M. Rein, "Proper Choice of the Measuring Frequency for Determining  $f_T$  of Bipolar Transistors", *Solid-State Electronics*, vol. 26, no. 1, pp.75–82, 1983.

- [16] Michael Schröter and Tzung-Yin Lee, "Physics-Based Minority Charge and Transit Time Modeling for Bipolar Transistors", *IEEE Transactions on Electron Devices*, vol. 46, no. 2, February 1999, pp288–300.